廣告

台積電創新測試電路設計 分析效率提升70%以上

【記者蕭文康/台北報導】面對日益複雜的半導體製程,台積電(2330)積極投入檢測技術研發與精進,透過優化晶片內的測試電路設計,提升研發人員進行失效故障分析的效率,可快速識別晶片及製程中的潛在風險,不僅成功減少實驗室端失效故障分析所需時間,亦能同步應用於製造端進行偵測與分析,進而縮短新製程學習曲線、加速良率達成;截至2025年9月,失效故障分析效率平均提升70%以上,以創新思維提升品質管理效能。

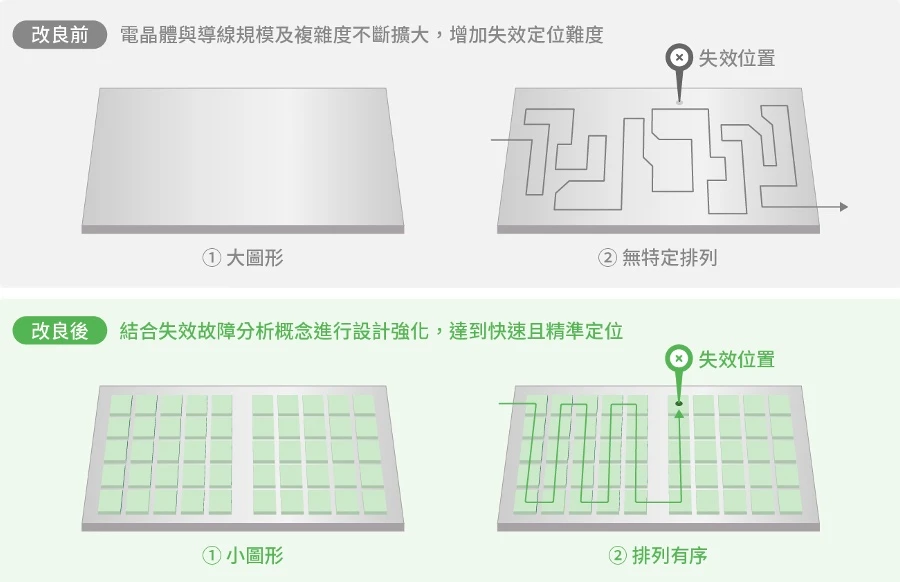

改良電路圖設計,突破失效定位挑戰

台積電表示,測試電路在半導體製程中扮演關鍵角色,可於晶片試製初期協助研發人員偵測失效並找出製程弱點,進一步調整開發流程。然而,隨著測試電路中電晶體與導線的規模及複雜度不斷擴大,失效定位的挑戰亦逐漸增加。

為提高處理效率,台積電採用設計強化策略,結合失效故障分析的概念,對測試電路進行全面優化。在符合測試項目的前提下,將原本電路圖中無序排列的大圖形,轉換為排列有序的小圖形,以達到快速且精準的失效定位;除於實驗室端應用外,亦同時部署至製造端,使產線上也能進行偵測與失效分析作業,增進生產效能及產品品質。

測試電路設計改良前後對比

台積電強調,公司以精益求精的品質文化為核心,透過改良測試電路設計,實現晶片品質與製程效能雙重提升,持續深化技術領先的競爭優勢,推動科技進步及永續發展的無限可能。