台積電封裝主管罕見受訪 外媒揭秘美製晶片100%全回台封裝真相

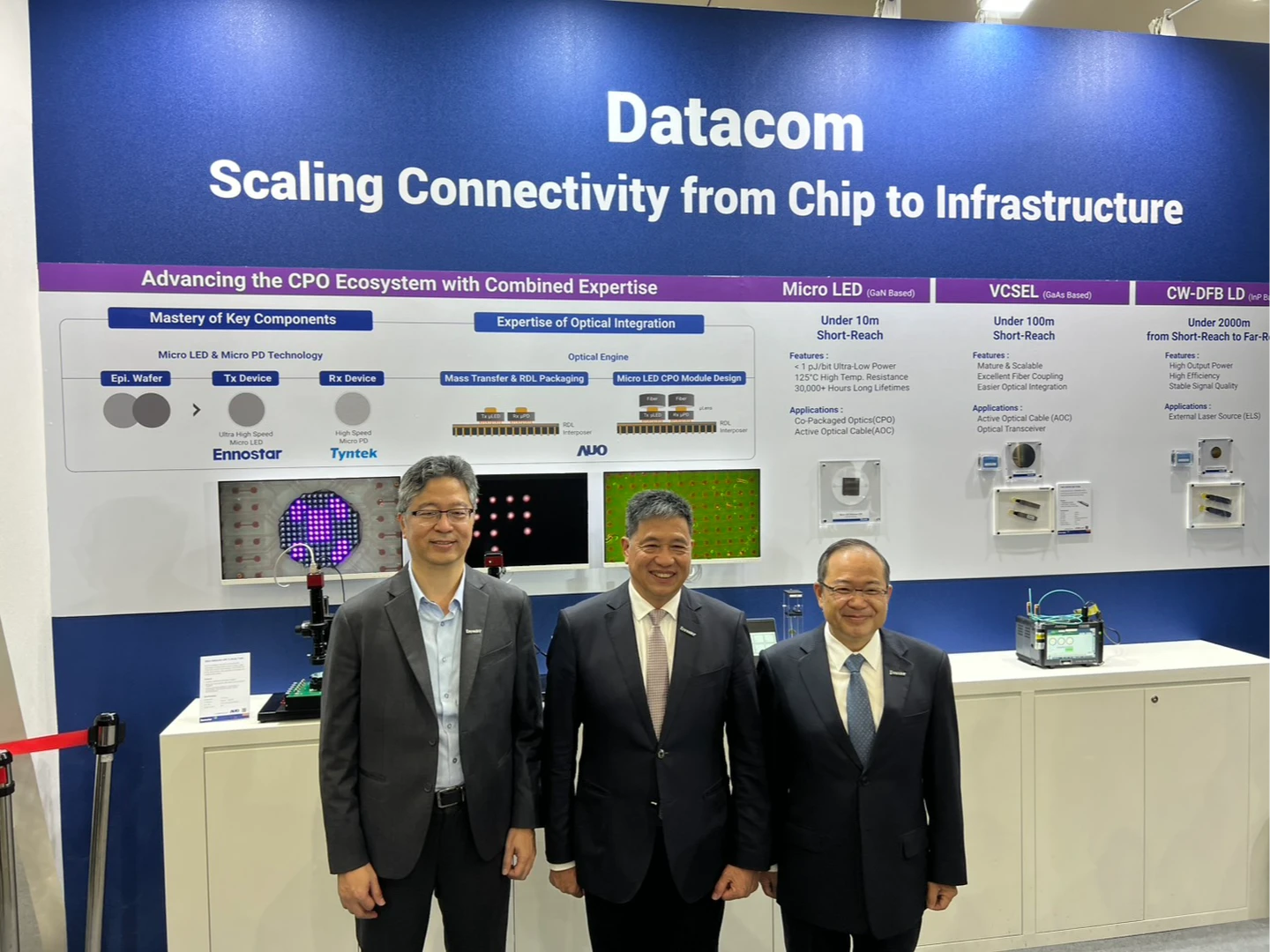

【編譯于倩若/綜合外電】台積電北美封裝解決方案主管Paul Rousseau近日罕見接受《CNBC》專訪指出,台積電目前最先進CoWoS技術正以約80% 年複合成長率快速成長,相關數據「正大幅提升」。他表示,該技術可將高頻寬記憶體更有效率地配置在運算晶片旁,提升整體效能,並形容這是摩爾定律向三維發展的自然延伸。

《CNBC》指出,目前台積電將100%晶片全部送回台灣進行封裝,即使是來自亞利桑那州鳳凰城先進晶圓廠的產品也是如此。台積電並未公布美國封裝廠完工的時間表。隨著台積電準備在亞利桑那州興建2座新廠,這項技術現在正成為焦點。

📌 本文摘要重點

(AI 摘要說明)台積電先進封裝技術與布局概況

Paul Rousseau:目前最先進CoWoS技術正以年複合成長率80%成長

《CNBC》在報導中探討「AI下一個瓶頸:為什麼即便是在美國製造的頂級晶片,也得繞一圈回台灣封裝」。

Paul Rousseau向《CNBC》表示,目前正在使用中最先進的方法是CoWoS,而他指出這項技術正以驚人的年複合成長率80%成長。他告訴《CNBC》,這些數字「正大幅成長」。

《CNBC》指出,輝達(Nvidia)已預訂了台積電大部分最先進的可用產能,而台積電在封裝領域的產量居於領先地位。隨著AI推動晶片製造商在推論運算硬體上追求更高密度、效能與效率,這項製程也因此備受關注。當電晶體密度逐漸逼近物理極限時,新的矽晶封裝方法就能提供幫助。

Paul Rousseau表示:「這其實就是摩爾定律往第三維度的自然延伸。」

AI產業下一個瓶頸:為何美國製造頂級晶片仍須往返台灣

數十年來,單一晶粒會從一整片晶圓上切割下來,再封裝成可連接電腦、機器人、汽車與手機等裝置的系統。隨著近年AI的興起讓晶片複雜度大幅提升,更先進的封裝技術也快速發展。

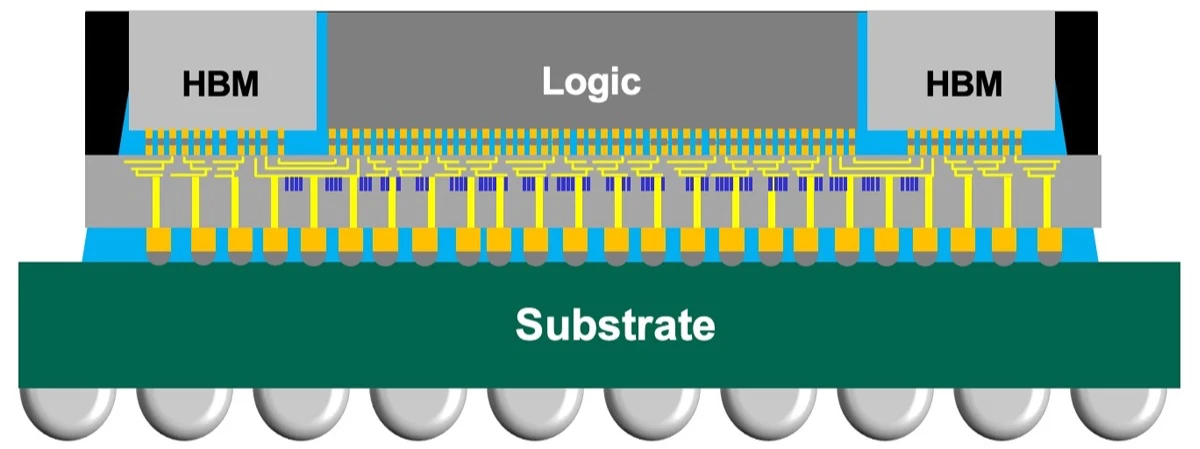

現在,會把多個晶粒(例如邏輯晶片與高頻寬記憶體)一起封裝成一顆更大的晶片,例如圖形處理器(GPU)。先進封裝用來把這些晶粒全部連接在一起,並讓它們彼此以及與整個系統互相傳訊。

輝達已預訂了台積電大多數領先的CoWoS技術產能,而且產能幾乎被訂滿,據報導台積電已將部分製程外包給專門處理較簡單步驟的第三方公司,例如日月光和艾克爾(Amkor)。此外,台積電也正在台灣擴建2座新的封裝廠,並在美國亞利桑那州興建2座封裝設施。

目前,台積電將100%的晶片送回台灣進行封裝,即使是來自亞利桑那州鳳凰城先進晶圓廠的產品也是如此。台積電並未公布美國封裝廠完工的時間表。

Paul Rousseau:導入CoWoS可將HBM直接置於運算核心旁,提高晶片效能

許多晶片(例如中央處理器)採用的是2D封裝;而像GPU這樣更複雜的晶片,則需要額外技術,也就是台積電的CoWoS,一種2.5D封裝形式。

對於這類晶片,會加入一層稱為中介層(interposer)的高密度導線層,提供更緊密連接,使HBM(高頻寬記憶體)可直接配置在晶片周圍,消除被稱為「記憶體牆」的瓶頸。

Paul Rousseau說明:「你根本無法在運算晶片內塞進足夠的記憶體來完全發揮它的效能,因此當我們導入CoWoS時,就能以非常有效率的方式,把HBM記憶體直接放在運算核心旁邊。」

Paul Rousseau:台積電採用SoIC封裝產品,還需要幾年時間才能看到

台積電在2012年率先推出2.5D技術,之後歷經多次迭代。台積電表示,輝達的Blackwell GPU是首個採用其最新一代CoWoS-L技術製造的產品。

同時,各大廠也在布局下一階段技術:3D封裝。英特爾(Intel)將其技術稱為Foveros Direct,而台積電的則稱為SoIC。

Paul Rousseau解釋:「過去是把晶片並排放置,現在則是把它們一層一層堆疊在一起。」他補充說,這樣可以讓它們幾乎就像是一顆單一晶片運作,進而帶來另一個層級的效能提升。

他表示,還需要幾年時間,我們才會看到台積電推出採用SoIC封裝的產品。